Cопроцессор Осина

Ученый из Сарова, Илья Осинин, создал сопроцессор, который в несколько раз лучше Intel.

Ученый из Сарова, Илья Осинин, создал сопроцессор, который в несколько раз лучше Intel.

Изобретение Ильи Осинина победило в конкурсе федерального уровня, а его создатель получил финансирование по Президентской программе исследовательских проектов.

Осинин является кандидатом технических наук. На конкурс Российского научного фонда от отправил свой «Модулярно-логарифмический сопроцессор для массовых арифметических вычислений».

«Разработка представляет собой аппаратный блок для отечественных процессоров, позволяющий проводить математические вычисления над вещественными числами в уникальной модулярно-логарифмической системе счисления», — объяснили специалисты ВНИИЭФ.

Как рассказал сам Осинин, его изобретение работает в паре с другим процессором.

Математику своего сопроцессора саровчанин разрабатывал специально под отечественные аппараты «Эльбрус-8С»,

«Байкал-М» и «KOMDIV-64».

Логарифмы саровский «сопр» в паре с отечественным процессорами считает в тысячу раз быстрее, чем Intel, а сложные полиномы — в 3 раза оперативнее, и все это при том, что тактовая частота западного процессора больше в 26 раз.

Важно отметить, что стоимость производства отечественной техники на 17% дешевле.

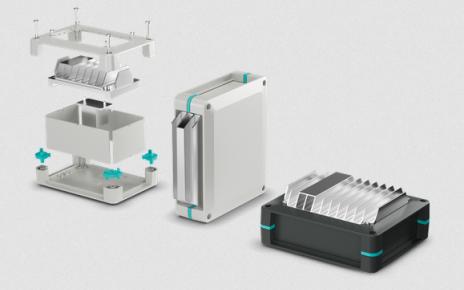

Предлагаемый сопроцессор представляет собой самостоятельный IP-блок системы-на-кристалле, позволяющий проводить математические вычисления над вещественными числами в уникальной модулярно-логарифмической системе счисления.

Обеспечены два уровня преобразования исходных чисел: в модулярную систему счисления вместо традиционной позиционной и в логарифмическую систему счисления вместо плавающей точки. Благодаря этому сопроцессор обладает более высоким быстродействием, точностью и надежностью вычислений по сравнению с известными аналогами. Он состоит из набора одинаковых вычислительных ядер, каждое из которых выполняет однотактовые скалярные или векторные операции.

Преобразование кодов в модулярно-логарифмическую систему счисления и обратно не вносит значительных временных задержек при большом потоке входных данных за счет предложенных аппаратных решений, конвейеризирующих процесс интерполяции функции логарифма и преобразования кодов системы остаточных классов. Реализован прототип устройства на базе программируемой логической интегральной схемы.